# Control Flow Integrity

Anti-Malware active protection on Arm64 Systems

# Executive summary

While major IT infrastructures are confronted with repeated ransomware and other cyberattacks, the security agencies call for help from the industry to stop the propagation of malware.

The cybersecurity chain of tools is now well established to detect and eradicate malware. From perimetric security on the network to behavioral security inside each system, each component provides its contribution to the security of large IT systems.

One loophole remains, however. When malware hits a system, after bypassing all protections ahead, the processor gently executes it, implicitly allowing the malicious payload to infect the system.

At SiPearl, we have one preoccupation : How can our processors fill that loophole? How can we actively contribute to anti-malware protection?

Following a careful analysis of the mechanisms through which malware finds its way into the system, this white paper describes how the Call Flow Integrity (CFI) techniques can prevent such intrusions.

The Arm64 CPU cores at the heart of the SiPearl processors offer unique CFI capabilities on the market. Two complementary features, Pointer Authentication Code (PAC) and Branch Target Identification (BTI), build a shield against the most dangerous forms of malicious code injection, those which exploit low-level software bugs and vulnerabilities.

This white paper describes in detail PAC and BTI, how they are defined by Arm, how to leverage their enormous potential, and how the current software implementations use them.

From an operating system perspective, the usage of PAC and BTI is described in Linux, macOS and Windows. The gcc and clang compilers are also examined, including the clang fork of Apple for macOS.

Lessons are learnt from this comparison. The most advanced and complete usage of PAC and BTI is observed in macOS and the corresponding clang fork. The way it works there demonstrates the power of the control flow integrity techniques in the Arm64 cores.

Based on this comparison, what remains to be done in Linux, gcc and mainstream clang becomes clear.

For the open-source communities who would volunteer to implement these improvements, or merge existing ones, or simply for the curious reader, two thirds of this white paper is a deep dive into the technical details of PAC and BTI.

Second release: October 2023

# Contents

| Exe  | ecutive | summary                                                               | 1  |

|------|---------|-----------------------------------------------------------------------|----|

| 1.   | Cybe    | rsecurity threats                                                     | 4  |

|      | 1.1.    | Defining the security target for SiPearl processors                   |    |

|      | 1.2.    | Prioritizing the threats                                              |    |

|      | 1.3.    | Role of the processor in the cybersecurity chain                      | 5  |

|      |         | 1.3.1. Anatomy of a malware                                           | 5  |

|      |         | 1.3.2. Tracking malware in the cybersecurity chain for IT systems     | 6  |

|      |         | 1.3.3. How the processor should contribute to the cybersecurity chain | 7  |

|      |         | 1.3.4. Malicious code injection techniques                            | 8  |

| 2.   | Arme    | 54 defensive security overview                                        | 10 |

|      | 2.1.    | Control Flow Integrity (CFI)                                          | 10 |

|      | 2.2.    | Available mechanisms in Arm64 architecture                            | 11 |

|      | 2.3.    | Impact on security and performance                                    | 11 |

|      | 2.4.    | Arm optional and mandatory features                                   | 13 |

|      |         | 2.4.1. Arm architecture profiles, versions, and features              | 13 |

|      |         | 2.4.2. Arm features for PAC and BTI                                   | 14 |

|      |         | 2.4.3. Arm features and the compilation dilemma                       | 15 |

|      | 2.5.    | Arm64 control flow integrity features in SiPearl processors           | 16 |

| 3.   | Cont    | rol flow integrity techniques in details                              | 16 |

|      | 3.1.    | Branch Target Identification (BTI)                                    |    |

|      |         | 3.1.1. BTI principles                                                 | 16 |

|      |         | 3.1.2. Backward compatibility                                         | 18 |

|      |         | 3.1.3. The BTI instruction                                            | 18 |

|      |         | 3.1.4. The PSTATE.BTYPE new processor state                           | 19 |

|      |         | 3.1.5. Compiler support                                               | 20 |

|      | 3.2.    | Pointer Authentication Code (PAC)                                     | 22 |

|      |         | 3.2.6. PAC principles                                                 |    |

|      |         | 3.2.7. Common PAC use case: function call                             |    |

|      |         | 3.2.8. PAC instructions                                               |    |

|      |         | 3.2.9. PAC cipher algorithms                                          |    |

|      |         | 3.2.10. PAC cipher keys                                               |    |

|      |         | 3.2.11. Four address spaces                                           |    |

|      |         | 3.2.12. PAC format and location in pointers                           |    |

|      |         | 3.2.13. Signature diversity                                           |    |

|      |         | 3.2.14. PACGA, a generic CMAC engine                                  |    |

|      |         | 3.2.15. Compiler support                                              |    |

|      |         | 3.2.16. Code generation influence on ROP : gcc vs. clang              |    |

|      |         | 3.2.17. Virtualization support (EL2)                                  |    |

|      |         | 3.2.18. Monitor support (EL3)                                         |    |

|      |         | 3.2.19. Handling software compatibility                               |    |

|      |         | 3.2.20. Comparative operating system support                          |    |

| 4.   | Furth   | er developments                                                       | 44 |

| Арр  | endix   | Relevant CPU system registers                                         | 45 |

|      | 2       |                                                                       |    |

| Refe | erence  | ۶                                                                     |    |

# 1. Cybersecurity threats

## 1.1. Defining the security target for SiPearl processors

The first generation of SiPearl processors is named Rhea. It targets the High-Performance Computing (HPC) market. It is specially designed to empower supercomputers for intensive computing.

The CPU cores in the Rhea processor are Arm Neoverse V1, which includes 256-bit vector computing units. In addition to traditional DDR memory, the Rhea processor embeds controllers for High-Bandwidth Memory (HBM), a high-end form of memory which is typically found in supercomputers.

The next generation of SiPearl processors will be twofold. First, there will be a successor to Rhea for the HPC market, with updated CPU cores and various improvements. Second, there will be a processor for the cloud and data center market.

This roadmap defines the security target for SiPearl processors : high-end HPC, cloud, data center, server systems and their environment.

This is a traditional IT-managed environment where the security is controlled by cybersecurity teams, using well-defined tools, in physically controlled environments.

Let's remark that, by contrast, embedded systems (IoT, mobile phones, etc.) are mobile, physically exposed to attacks. Their threat model is very different and includes ranges of physical attacks on the hardware components: invasive attacks (glitch, laser) or side channel attacks (power, temperature). This well-known threat model in the hardware community does not apply to HPC, cloud or data centers.

A careful definition and analysis of the threat model for the SiPearl processors and the corresponding security priorities are initial requirements to define the right security solutions.

## 1.2. Prioritizing the threats

What are the topmost important threats in IT systems?

How can a processor contribute to mitigate these threats?

These are the two important questions a modem processor for IT systems should answer.

It is the role of the national and international security agencies to identify the top-priority threats. These agencies operate in the field. They respond to actual threats. They fix real problems. They have learnt to identify the malicious actors, their motivations, their mode of operation.

What do they say?

Jen Easterly, head of CISA, USA [24]:

We cannot have the same sort of attacks on hospitals and school districts that we've been seeing for years. We have to create a sustainable approach to cyber safety.

Guillaume Poupard, former head of ANSSI, France [25]:

Hospitals, institutions, corporations, and all sectors are impacted by hackers. The number of attacks has multiplied by ten in three years. And this is probably a small part of reality.

The security agencies call for action. They request the cybersecurity community to fight criminal activities, to stop cyber-attacks. Cyber-criminal activities are real, current, frequent. They hurt our countries, the institutions, the national corporations, and society in general.

The most important vectors of cyber-attacks have been known for years: all sorts of malware propagate over networks, through direct attacks, phishing, social engineering, tricking computers or users to download or accept incoming malicious data, turning them into malware exploiting software vulnerabilities.

How can a processor help in this cybersecurity fight?

## 1.3. Role of the processor in the cybersecurity chain

#### 1.3.1. Anatomy of a malware

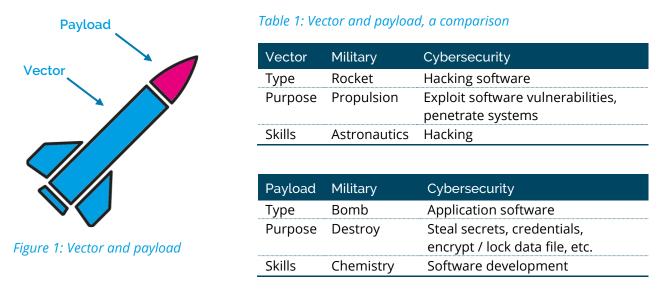

In cybersecurity, it is common to describe malware in terms of *vector* and *payload*.

This terminology is inspired by the military, from the structure of a missile.

In both cases, the military and cybersecurity, the vector is a vehicle which transports the destructive payload into the territory of the target.

In the fight against an attack, it is equally useful to counter the vector and the payload. However, different components in the system more easily address one or the other.

Let's review now where the processor can be useful.

## 1.3.2. Tracking malware in the cybersecurity chain for IT systems

In large IT systems, most of the cybersecurity chain is made of software. When the term *hardware* is used, it often designates a *network security appliance*, a closed system with security software running on it. There is no or little *hardware security*, as the term is used in embedded systems (mitigate physical attacks).

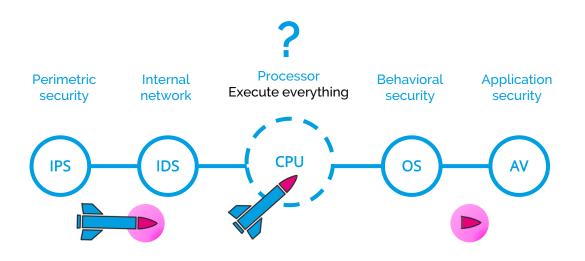

The way malware is tracked all along the chain is summarized in Figure 2 below.

- Perimetric security is the first line of defense. Intrusion Prevention Systems (IPS) and firewalls integrate malware detection systems and try to prevent their intrusion in the network.

- The internal network security is made of Intrusion Detection Systems (IDS). A Security Information and Event Management system (SIEM) centralizes the events and reports alerts, such as detected malware.

- Inside each server or desktop system, behavioral security includes integrity checks on the operating system and applications, applies heuristics on the running system to detect suspect activities, possibly with the help of Artificial Intelligence (AI) techniques.

- At the end of the chain, application security includes antivirus products which permanently inspect the file systems to detect malware.

**Note:** Modern forms of IT cybersecurity, such as Zero Trust (ZT) architecture, focus on authentication. Instead of considering the network as a trusted area, authentication is centralized, and identification is enforced virtually everywhere. However, ZT does not address malware detection. In IT infrastructures with ZT authentication, the fight against malware infection remains the responsibility of detection tools.

Figure 2: The current malware detection chain

Two interesting facts emerge from this description:

- Most detection tools focus on the malware payload. The viral charges are detected, either statically using sets of signatures, or dynamically based on their suspect behavior. No or few tools can detect or block the malware vectors, the penetration subset of the malware.

- Inside server systems or desktop systems, the processor has no security added value so far. A

processor just executes instructions, equally, sequentially, one after the other, without checking,

without wondering if it executes the operating system, an application, or some malware.

Clearly, the processor can do better.

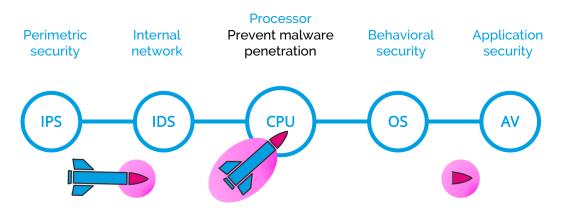

## 1.3.3. How the processor should contribute to the cybersecurity chain

The processor is the component which is directly hit by malware vectors.

The purpose of the malware vector is to penetrate a system. It starts with a legitimate application or network stack which manipulates the incoming malware as simple data. Then, the malware exploits security vulnerabilities in the legitimate software to force the execution of the vector, then the payload.

What is a security vulnerability? Most of the time, this is a software bug that a hacker turns into a vulnerability, a way of penetrating the system.

We can classify these software bugs in two categories:

- High-level software bugs: design or configuration errors which open the doors of the system.

- Low-level software bugs: input validation failure or buffer overflow which are turned into code injection by hackers.

An example of design error is Log4j [27], a logging framework which, by design, allows the download and execution of arbitrary code. Examples of configuration errors are weak passwords, default passwords, opened network ports.

These high-level errors are mostly due to a lack of methodology. Security awareness is continuously increasing in the software industry, and we observe a slow but constant decrease in this type of threat.

Low-level bugs, on the other hand, are much more difficult to track and eradicate. Most of them are small programming errors, with devastating consequences. Even though more robust programming languages and tools exist, programmers are humans and low-level software bugs will likely never disappear.

This is where the processor can help.

This is the added value of the processor in the cybersecurity chain.

The processor is the only component in the system which is in direct contact with malware vectors. The processor is in a unique position to detect malware vectors in action and block them before penetration. Thus, the processor fills the hole in the security chain.

Figure 3: Active role of the processor in the malware detection chain

Detecting malware vectors is obviously not sufficient to prevent all malware injections. Typically, the processor cannot detect misconfigured systems which allow arbitrary code injection. In the security chain, no component can guarantee the security of the system alone. However, each component has a role to play. The security of the system is guaranteed by the combination of these individual roles. The purpose of this paper is to define the role of the processor in the cybersecurity chain.

Let's now review how malware takes advantage of these low-level software bugs to inject malicious code. Then, in the next chapter, we will see how the processor can block these attacks using defensive security techniques.

## 1.3.4. Malicious code injection techniques

Code injection is the art of turning malicious data into malware code execution.

The most common root cause is a software bug (input validation failure, insufficient memory management) causing a buffer overflow in a legitimate – but buggy – application. The buffer overflow overwrites memory containing pointers to code. When an indirect branch is taken using these code pointers, unexpected code is executed.

The art of hacking consists in subverting existing branch instructions to jump into code which is controlled by the hacker.

Buffer overflow exploitation techniques have been abundantly documented, although essentially on Intel CPU architecture. See examples in [29], [30], [31], [32].

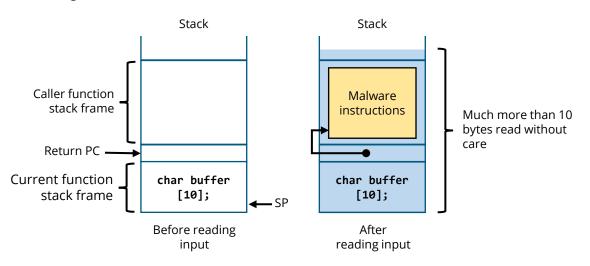

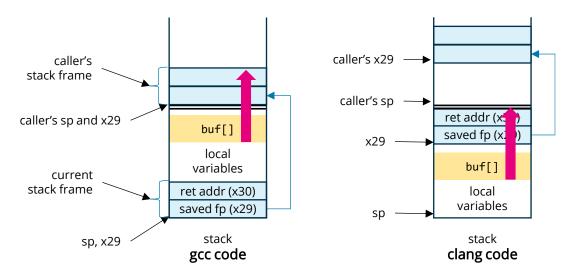

#### Historical methods: direct code injection on stack

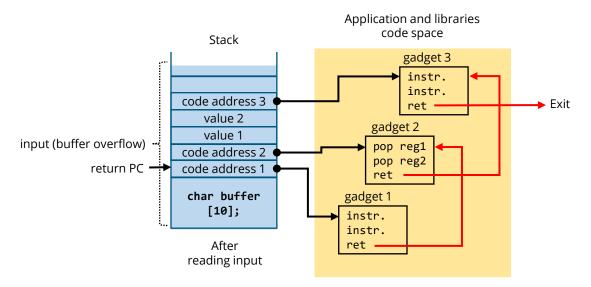

The original code injection technique is as old as the Morris worm in 1988 [26]. This typical software bug is illustrated on Figure 4 below.

#### Figure 4: Older direct code injection techniques on stack overflow

Some function in the application reads a variable-length data structure from an input source which can be controlled by the attacker (a document file, a network connection). By specification of the protocol, this data structure is limited to 10 bytes for instance. The application consequently allocates a 10-byte local buffer (on stack). Because of a bug, the application fails to validate its input. If the data announces a much larger size, say 100 bytes, the application blindly reads those 100 bytes. This causes a buffer overflow, overwriting the memory beyond the input buffer.

On most CPU architectures, the stack expands to descending addresses. Overflowing a local buffer on stack means overwriting the return address to the caller. After the buffer overflow, when the function which performed the input operation returns, the processor pops the return address from stack and jumps to the corresponding code address. If that address was trashed with garbage, the program would likely crash.

However, in the case of a carefully crafted attack, the hacker includes the malicious code in the overflown input data and places the address of this code in the middle, where the return address is expected. Thus,

on return, the function simply jumps into the hacker's code. This is how we turn passive input data into executed code.

This was a long time ago.

Since then, most operating systems turn the stack into "non-executable mode" in the page tables of the virtual memory system. When the historical direct attack is attempted, the application crashes when the processor attempts to execute an instruction from the stack.

#### Modern techniques: return-oriented programming (ROP)

As hackers are quite good at mitigating countermeasures, they quickly found a workaround.

In the early 2010's, they invented the Return-Oriented Programming (ROP) techniques. Since data areas were all protected against execution, it was no longer possible to directly inject code as data. However, in the meantime, the applications became so complex that the virtual address space of any application contains megabytes of legitimate code pages, from the application, from the libraries it uses, from the other libraries which are used by the libraries, etc.

It may seem weird, but it is easy to cut a potential malware code into small blocks of instructions which can be found in memory, in the megabytes of legitimate code pages. The condition is that each small block is terminated by a "return" instruction or equivalent.

Each return-terminated piece of legitimate code is called a *gadget*. Starting from a piece of malware code, automated tools can slice it into gadgets, searching into the binaries of the application and all shared libraries which are recursively activated. Such tools are named *gadget finders*.

#### Figure 5: Simplified 3-gadget ROP chain attack

Once the list of addresses of these gadgets is built, just inject it in reverse order in the buffer overflow attack, starting at the address of the first return address. When the buggy function which causes the buffer overflow returns, the processor jumps to the first gadget in the list. Since this gadget terminates with a return instruction, the processor naturally pops the address of the second gadget and jumps to it. And so on...

Of course, depending on the CPU architecture and its ABI, the exact layout of the buffer overflow area may be slightly more complex than a simple list of addresses. But the principle remains the same.

This is illustrated in Figure 5 above.

Again, this technique may seem weird, but it works. If you are skeptical, just google for "ROP gadget finder".

To counter these techniques, most operating systems have introduced the concept of Address Space Layout Randomization (ASLR). Each time a process is created, the main executable and all libraries are mapped in virtual memory at random addresses. Thus, it is more complicated to predict the virtual address of an identified gadget. However, there are a few constraints. Exactly all compilation units in the application and the libraries must be compiled with position-independent code. This is not always possible. Even if the amount of legitimate code at predictable virtual addresses is smaller with ASLR than without it, it does not completely prevent ROP attacks.

In addition to ROP attacks which are based on buffer overflow on stack to exploit return instruction, there is a variant named Jump-Oriented Programming (JOP). It exploits buffer overflow elsewhere, typically on the heap. The idea is to overwrite code pointers from code dispatch tables of C++ vtables and then wait for the application to call the corresponding code.

Let's now review how the defensive security features of the Arm64 architecture can help prevent these attacks.

## 2. Arm64 defensive security overview

The security architecture of a system can be divided into *security by design* feature and *defensive security* features. The two sides are equally important to guarantee the security of the system.

Security by design is a theoretical top-down approach which defines the security architecture, the roles of all actors in the system, the security boundaries, and the isolation mechanisms. In the Arm architecture, security by design mechanisms include TrustZone [6] for embedded systems and Confidential Compute Architecture (CCA) [7] for server systems.

Defensive security, on the other hand, is a pragmatic bottom-up approach which addresses actual security situations, after all other security mechanisms were broken or avoided.

Preventing low-level code injection at processor level is part of defensive security. It stops the malware injection at the last moment, after all upstream malware detection tools were deceived, after bugs in legitimate application code were exploited to inject code.

## 2.1. Control Flow Integrity (CFI)

Malware code injection using ROP and JOP attacks can be tracked down to a unique common cause: branching at unexpected code locations.

In practice, legitimate code runs in an application or in the operating system. This legitimate code has an expected call flow, where branch instructions jump to some expected locations. However, at some point, because of some software bug, the processor suddenly branches to an unexpected location, typically in some sequence which represents the malware code.

Differentiating legitimate and unexpected branches in the code is called Call Flow Integrity (CFI).

Using CFI techniques, a processor can:

- mitigate Return-Oriented Programming (ROP) attacks, typically from buffer overflows on stack,

- mitigate Jump-Oriented Programming (JOP) attacks, typically from buffer overflows on heap.

Adding CFI capabilities to a processor usually requires improvements in the Instruction Set Architecture (ISA), the compilers and the kernel of the operating system.

Many CFI research projects exist around the globe. They define extensions to common ISA's such as Intel, MIPS, Arm, RISC-V. The most complete research project is CHERI (Capability Hardware Enhanced RISC Instructions) from the University of Cambridge and SRI International [18]. This is a multi-architecture project which proposes extensions to Intel, MIPS, Arm, or RISC-V. In the RISC-V community, many competing CFI projects exist.

In production, available today in current processors, the Arm64 architecture probably provides the most efficient set of Control Flow Integrity features.

## 2.2. Available mechanisms in Arm64 architecture

The CFI features in the Arm64 architecture are implemented using two complementary mechanisms:

- Pointer Authentication Code (PAC)

- Branch Target Identification (BTI)

PAC focuses on the source of branch instructions.

Using PAC, all pointers, to code and data, can be *authenticated*. A common technique of code injection consists in altering some memory location which contains a pointer to code. Any alteration of these locations results in the later execution of some unexpected code. The purpose of PAC is detecting these alterations through authentication mechanisms.

PAC will be described in detail in section 3.2.

BTI focuses on the target of branch instructions.

In most code, very few instructions are targets of legitimate branches. On the other hand, most gadget entry points in ROP and JOP attacks are not the target of any legitimate branch. Using BTI, legitimate targets are clearly identified. Branching to any other instruction is a clear symptom of code injection attack and results in an exception.

BTI will be described in detail in section 3.1.

PAC is supported on Armv8.3-A onwards, with gcc 7.1, clang 8.0, and the Linux kernel 5.0 (in user code) or 5.14 (in kernel code).

BTI is supported on Armv8.5-A onwards, with GCC 9.1, clang 8.0, and the Linux kernel 5.8.

## 2.3. Impact on security and performance

As usual, there is a trade-off between security and performance. The optimal solution is obtaining the highest level of security with the lowest impact on performance.

As we will see later in this document, most of the magic is in the compiler. Based on the current state of the compilers, Arm did some benchmarking which are summarized below. Considering that these results were established by Arm, they should be interpreted with some precaution. However, experience demonstrates that they are very close to reality.

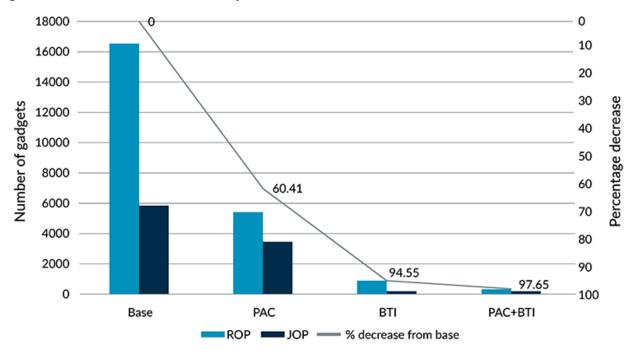

The security benefit is measured by the number of remaining potential gadgets in standard applications and libraries.

The exercise was done on the GLIBC library, using PAC, BTI or a combination of the two. Without any of them, all instructions in the GLIBC code are potential gadget entry points. With BTI, only explicit BTI instructions can be used as gadgets by JOP attacks. With PAC, return instructions can no longer be used as ROP attacks<sup>1</sup>.

The results of the Arm's benchmarks are summarized in Figure 6 below. Using PAC+BTI, the number of gadgets which are available is reduced by 97.65%.

*Figure 6: ROP and JOP gadgets in GLIBC* © *Arm* [2]

There are no precise details on the test methodology to locate potential gadgets. Nonetheless, these results are credible. The only surprising point is the benefit of BTI alone, without PAC. It could be expected to have a larger impact on JOP attacks and a lower impact on ROP attacks.

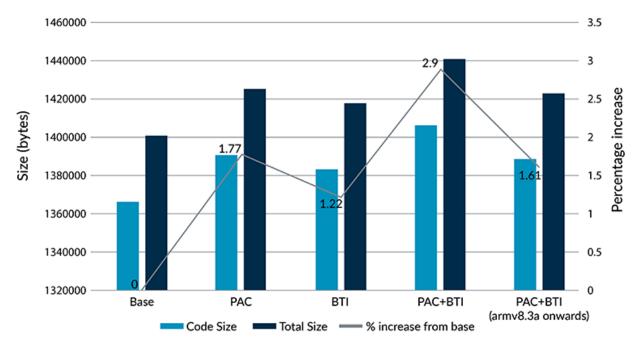

The impact on code size has been evaluated by Arm on the GLIBC library as well. The results are summarized in Figure 7 below.

With PAC+BTI protection the increase of code size is 2.9% with backward-compatible code and only 1.6% when the code is compiled for Armv8.3-A or higher.

As explained in the next sections of this paper, PAC and BTI features are implemented starting with versions v8.3 and v8.5 of the Arm architecture, respectively. It is possible to generate code which is backward compatible on older versions of the architecture. In that case, the added instructions behave as NOP on older CPU cores. However, the code generation is limited to a subset of the PAC features and generates more instructions (larger code).

When the code is specifically compiled for Armv8.3-A onwards, new and more compact instructions can be used instead.

Therefore, it is recommended, when possible, to generate specialized binaries for Armv8.3-A onwards. The resulting binaries have less instructions, they are faster, and they potentially protect against a wider range of ROP and JOP attacks.

<sup>&</sup>lt;sup>1</sup>PAC could be used to mitigate a larger number of attacks but, currently, Linux does not implement that kind of protection, only macOS does. See more details later in this document.

Note that BTI is fully backward compatible and fully independent of the CPU core. The right selection of the compilation target matters with PAC only.

#### Figure 7: Change in image size from enabling ROP and JOP mitigation © Arm [2]

The impact on performance was not evaluated in Arm's benchmark. It is the direct consequence of the execution of the additional instructions. Therefore, the impact on performance depends on the implementation of each CPU core and cannot be evaluated in the general case.

However, the added instructions for PAC and BTI are straightforward. They do not involve any form of branch (except when they generate an exception) and probably do not break any form of speculative execution. Therefore, the performance impact is directly related to the number of added instructions.

In the *Arm Software Optimization Guides* for the Neoverse N2 [5], V1 [3], and V2 [4] CPU cores, the PACxx and AUTxx instructions have a latency of 5 cycles. This is between an integer multiplication (2 to 4 cycles) and an integer division (5 to 20 cycles).

PAC instructions are also sensitive to the speed of the underlying cipher algorithm. Several algorithms are allowed. CPU cores using the QARMA3 algorithm instead of QARMA5 may expect a small performance benefit, at the expense of security. All initial Arm-designed cores such as the Neoverse V1 implement QARMA5. This is explained in detail in section 3.2.9.

## 2.4. Arm optional and mandatory features

## 2.4.1. Arm architecture profiles, versions, and features

The Arm architecture is flexible and available in many flavors.

At a high level, there are several *profiles* for distinct classes of devices. The M-profile addresses small mobile devices. The A-profile addresses application processors. In this paper, we only consider the A-profile, as used in server-class systems.

In each profile, successive *versions* are defined. In 2023, existing 64-bit processors implement versions Armv8.0-A to Armv8.5-A. At the architecture specification level, the latest version is Armv9.2-A, although it is currently not yet implemented in any CPU.

In each profile and version, several *features* are specified. Each feature has a name in the form FEAT\_xxx.

Features are specified as optional starting at some version and possibly mandatory starting at some other higher version.

As of Armv9.2-A, the architecture defines 244 features [21].

Identifying the exact set of features that an Arm-based core implements is not as easy as it seems. For Arm-designed cores, the Technical Reference Manual (TRM) does not provide a precise list of all FEAT\_xxx for that core. Out of 244 Arm features, 224 can be detected from software [20] but software can be run only if a chip is already available with that core.

#### 2.4.2. Arm features for PAC and BTI

The Table 2 below lists all Arm features which implement PAC and BTI.

#### Table 2: Arm features for PAC and BTI

| Feature            | Optional | Mandatory | Description                                                                           |

|--------------------|----------|-----------|---------------------------------------------------------------------------------------|

| FEAT_BTI           | —        | Armv8.5A  | Branch target identification                                                          |

| FEAT_PAuth         | —        | Armv8.3A  | Pointer authentication                                                                |

| FEAT_PAuth2        | Armv8.3A | Armv8.6A  | Enhanced pointer authentication: XOR PAC with upper bits                              |

| FEAT_CONSTPACFIELD | Armv8.3A | —         | Enhanced pointer authentication: use bit 55 to compute PAC size and location          |

| FEAT_EPAC          | Armv8.3A | —         | Enhanced pointer authentication: set PAC to zero<br>on non-canonical addresses        |

| FEAT_FPAC          | Armv8.3A | —         | Fault on pointer authentication failure (AUTxx)                                       |

| FEAT_FPACCOMBINE   | Armv8.3A | —         | Fault on pointer authentication failure in combined instructions (RETAA, LDRAA, etc.) |

| FEAT_PACIMP        | Armv8.3A | _         | Pointer authentication: implementation-defined algorithm (e.g., Apple cores)          |

| FEAT_PACQARMA3     | Armv8.3A | —         | Pointer authentication: QARMA3 algorithm<br>(3-round QARMA64)                         |

| FEAT_PACQARMA5     | Armv8.3A | —         | Pointer authentication: QARMA5 algorithm<br>(5-round QARMA64)                         |

PAC is made of a set of complementary features, some of them are mandatory, some others are optional. BTI, on the other hand, is simpler in principle and made of one single feature.

These features are materialized by new mechanisms in the CPU cores.

New system registers:

Five 128-bit registers for PAC cipher keys.

New virtual memory management features:

- BTI guarded pages.

- Virtual address manipulation (PAC and/or MTE<sup>2</sup> tag in upper bits).

The new instructions can be classified as follows:

- 49 new instructions<sup>3</sup> (48 for PAC, 1 for BTI).

- 14 new instructions are "hints", they act as a NOP on CPU cores which don't support the feature.

- These instructions provide backward compatibility.

- BTI is fully backward compatible.

- 35 new instructions are not hints.

- Software may need two binary packages, one is fully backward compatible, the other is more secure, faster, more compact, but not backward compatible.

This very last point introduces a new issue: the compilation dilemma.

#### 2.4.3. Arm features and the compilation dilemma

A target platform is defined by the features which are implemented in the CPU core. This set of features has an impact on the compilation and code generation, mostly because some features define new or specific instructions. Executing these instructions on a CPU core which does not implement the corresponding feature results in an illegal instruction exception.

To address the diversity of CPU cores, there is a compilation dilemma with two options:

- Compile each application for a specific target, using the right compilation options for the features of the target CPU core.

- Compile generic binaries which do not use specific instructions, or only the backward-compatible ones, just using the basic common Arm features.

The first option is typically used in embedded systems. The target is well defined, and the corresponding Software Development Kit (SDK) is specifically tuned for that target.

In the server, cloud, or even desktop market, the requirements are different. Users do not compile for the target. Most of the time, they don't even compile at all. They download binary packages for Linux Ubuntu, Red Hat, or some other distribution (letting aside Windows or macOS) and they expect the system to work at the best of its capabilities.

In this context, the current approach is the second option of the compilation dilemma: provide a common, compatible, set of binary packages.

As of mid-2023, the binary Linux kernels which are installed with recent versions of Ubuntu, Debian, Fedora, are built with the backward-compatible subset of PAC. This is better than nothing, but not much. Applications and libraries are not compiled with PAC or BTI.

This is not satisfactory. There is a huge potential for security improvements in Armv8.3-A onwards. Armv9-A will add even more. What's the use of having such a potential if we do not use it?

On the other hand, building a completely protected binary system won't work on older Arm systems.

This problem was not perceivable when Arm CPU cores were used in embedded devices only because of the "compile for the target" rule. Now that Arm is used in larger, generic systems, the open-source community should tackle that problem.

<sup>&</sup>lt;sup>2</sup> MTE is the Memory Tagging Extension, a debug feature to track the usage of memory.

<sup>&</sup>lt;sup>3</sup> The Armv9.2-A ISA defines more than 1600 instructions, vector (SVE) and matrix (SME) extensions included.

Binary distributions should be produced for a few predefined target profiles, for example: basic Armv8.0-A systems, CFI-protected Armv8.3-A systems (full PAC+BTI support) and maybe CCA-enhanced Armv9-A systems in the future.

This is not new. There was a time when distinct packages were available for i386 and i686 targets. The i386 packages could work on any x86 system but ignoring the additional capabilities of i686 systems was considered not satisfactory.

## 2.5. Arm64 control flow integrity features in SiPearl processors

As mentioned in section 1.1, Rhea, the first generation of SiPearl processors, addresses the HPC market. It is based on Arm Neoverse V1 cores. This core implements the Armv8.4-A architecture. As such, it includes PAC features but not BTI.

The exact list of CFI features in Neoverse V1 is the following: FEAT\_PAuth, FEAT\_PAuth2, FEAT\_EPAC, FEAT\_PACQARMA5.

The next generation of SiPearl processors will target the cloud, data center and server market. These processors use CPU cores at Armv9.0-A and Armv9.2-A levels. They implement all PAC and BTI features and are particularly suited to enhance the cybersecurity chain of the data centers by mitigating malware injection attacks.

From a security perspective, these Armv9 cores also implement the Arm Confidential Computer Architecture (CCA). It defines a powerful model of hardware segmentation between so-called "realms" (think "virtual machines"). This segmentation is most wanted in cloud environments where complete strangers share the same physical infrastructure.

This exciting security topic can be described as "security by design" or "proactive security" and will be addressed in a separate white paper.

# 3. Control flow integrity techniques in details

The last part of this white paper dives into the gory details of PAC and BTI on Arm64 processors. If you just want an overview of control flow integrity techniques, it is not necessary to read it. On the other hand, if you want to improve the compilers or the Linux kernel to take full advantage of PAC (there is a lot of room for improvement), this is a recommended reading.

Although it is common to mention PAC+BTI in this order, let's start with BTI for one simple reason: it is simpler than PAC.

## 3.1. Branch Target Identification (BTI)

#### 3.1.1. BTI principles

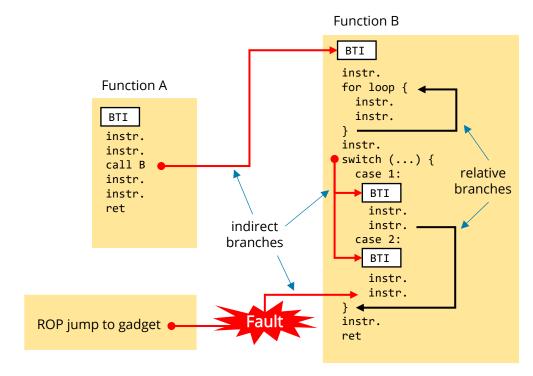

BTI focuses on the target of illegitimate jump operations.

How can an existing branch instruction perform an illegitimate jump? First, it is worth noting that there are two types of branch instructions: direct and indirect.

In an ISA with fixed-length instruction such as Arm64, all direct branch instructions are *relative*. It reads, for instance, "*branch 136 bytes ahead of current program counter*". Since code pages are read-only, they cannot

be altered and the offset value "136" in the example is hardcoded in the instruction. Thus, direct branches are always legitimate and not subject to code injection.

Indirect branches, on the other hand, are vulnerable. When an instruction is jump or call at address from register X16, for instance, we do not know where the content of this register comes from. It has probably been loaded or computed from a memory location. This location may have been altered by a buffer overflow.

This is why the BTI mechanism only focuses on indirect jumps.

In real code, very few instructions are legitimate targets for indirect jumps. There are the function entry points, the various branches of switch / case structures with a dispatch table, and a few other corner cases. That's all. In practice, this represents approximately 1% of all instructions (1.22% in GLIBC, according to Figure 7, page 13).

On the other hand, an illegitimate jump into a gadget is a branch at some arbitrary location, where no legitimate indirect jump is supposed to land.

The idea behind BTI is to clearly identify which instructions are valid targets for indirect jumps (1% of the code) and which are not (99% of the code).

In practice, a new instruction named BTI is introduced. This is just a placeholder. Functionally, this is a NOP. However, it identifies a legitimate target for an indirect branch. The compiler adds a BTI instruction wherever it generates code for such a legitimate target.

During execution, the processor carefully checks that all indirect jump instructions land at a BTI instruction. Otherwise, trying to branch to any other instruction is a clear symptom of ROP or JOP attack and a fault is generated.

This is illustrated in Figure 8 below.

Figure 8: Branch target identification principles

We can see that relative branches do not need a BTI instruction since they are hard-coded and cannot be circumvented.

A ROP jump into a gadget, on the other hand, is an indirect jump to an arbitrary instruction which is not a BTI 99% of the time and will generate a fault.

What about the remaining 1%? There is indeed a 1% risk of having a gadget starting at a BTI instruction. However, gadgets are small pieces of code. Executing a complete malware bootloader means chaining N gadgets. And the probability of having N gadgets in a row starting with BTI is 0.01<sup>N</sup>, which tends to zero when N grows.

#### 3.1.2. Backward compatibility

#### Hardware backward compatibility

To address hardware backward compatibility, the BTI instruction has been allocated in the HINT range. This means that CPU cores which do not implement BTI (typically before Armv8.5-A) simply ignore the BTI instruction.

This is why it is recommended to compile all new code with BTI instructions. It will run on all Arm64 processors.

#### Software backward compatibility

Not all existing code is compiled with BTI instructions. Legacy applications were built with no BTI, and we still need to run them on recent CPU cores with BTI support.

To support this use case, the Armv8.5-A architecture introduces the concept of *guarded page*. The guarded page indicator is a bit in the page tables of the virtual memory system (just like the non-execute bit). Filtering indirect jumps on BTI is active only if the target instruction is in a guarded page. Otherwise, indirect jumps are allowed to land anywhere in a non-guarded page.

In practice, when the compiler generates BTI instructions, it marks the code as such. When the linker grabs all modules (which may have been separately compiled with or without BTI), it groups code with BTI in guarded pages and code without BTI in non-guarded pages. Legacy application binaries have no guarded pages.

Thus, the complete backward compatibility and interoperability between old and new code is guaranteed.

#### 3.1.3. The BTI instruction

Let's now study the BTI instruction in detail.

BTI is not simply a generic landing place for indirect jumps. It is possible to filter which types of indirect jump are allowed here. For this finer level of filtering, the BTI has a 2-bit operand with four possible values, as illustrated in Table 3 below.

#### Table 3: BTI operand

| Instruction | HINT    | Operand | Description                                                       |

|-------------|---------|---------|-------------------------------------------------------------------|

| BTI         | HINT 32 | 00      | No branch is allowed to land here (not used in practice)          |

| BTI c       | HINT 34 | 01      | Only calls ("c") are allowed to land here (BLR-type instructions) |

| BTI j       | HINT 36 | 10      | Only jumps ("j") are allowed to land here (BR-type instructions)  |

| BTI jc      | HINT 38 | 11      | Calls and jumps are allowed to land here                          |

Thus, the entry point of a function is a "BTI c" instruction while the first instruction of a switch / case branch is a "BTI j" for instance.

#### 3.1.4. The PSTATE.BTYPE new processor state

Starting with Armv8.5-A, a new 2-bit processor state named PSTATE.BTYPE has been introduced.

The processor state is set by each instruction and describes the "branch type" of the current instruction. The possible values of PSTATE.BTYPE are presented in Table 4 below.

#### Table 4: How PSTATE.BTYPE is set by instructions

| Executed instruction                     | From region | Register used        | PSTATE.BTYPE |

|------------------------------------------|-------------|----------------------|--------------|

| BLR, BLRAA, BLRAAZ, BLRAB, BLRABZ        | Any         | Any                  | 10           |

| BR, BRAA, BRAAZ, BRAB, BRABZ             | Guarded     | Any, except X16, X17 | 11           |

| BR, BRAA, BRAAZ, BRAB, BRABZ             | Guarded     | X16, X17             | 01           |

| BR, BRAA, BRAAZ, BRAB, BRABZ             | Non guarded | Any                  | 01           |

| RET, RETAA, RETAB                        | Any         | Any                  | 00           |

| Other instructions (non-indirect branch) |             |                      | 00           |

We can interpret PSTATE.BTYPE as follows:

- 00 : not an indirect branch (except RET), no branch hijacking is possible.

- 10 : indirect branch to subroutine.

- 11 : indirect branch from controlled code, i.e., from a guarded page, not using X16/X17 (IP0/IP1).

- 10 : indirect branch from uncontrolled code, i.e., from non-guarded page or using X16/X17.

As a general rule, all indirect branch instructions set PSTATE.BTYPE to a non-zero value (with the notable exception of return instructions).

#### Table 5: BTI operand / PSTATE.BTYPE compatibility

| BTI operand | BTYPE = 00<br>Not hackable | BTYPE = 01<br>Jump from uncontrolled | BTYPE = 10<br>Call function | BTYPE = 11<br>Jump from controlled |

|-------------|----------------------------|--------------------------------------|-----------------------------|------------------------------------|

| 00 (none)   | Not compatible             | Not compatible                       | Not compatible              | Not compatible                     |

| 01 (c)      | Compatible                 | Compatible                           | Compatible                  | Not compatible                     |

| 10 (j)      | Compatible                 | Compatible                           | Not compatible              | Compatible                         |

| 11 (jc)     | Compatible                 | Compatible                           | Compatible                  | Compatible                         |

When the next instruction to be executed is inside a guarded page, PSTATE.BTYPE is checked. When this state value is non-zero (i.e., the processor executes some form of indirect branch), a *branch target exception* is generated, unless the instruction is one of:

- BTI instruction with a compatible PSTATE.BTYPE (see Table 5 above)

- BRK instruction (breakpoint exception)

- HLT instruction (debug event)

- PACIASP, PACIBSP with

- PSTATE.BTYPE = 01 or 10

- PSTATE.BTYPE = 11 and SCTLR\_EL1.BT0/1 = 0 (plus additional control by hypervisor and monitor through SCTLR\_EL2 and SCTLR\_EL3)

The reason for the very last rule on PACIxSP instructions is unclear. Maybe it was specified to avoid a BTI instruction when a function starts with a PACIxSP instruction.

Note: RET instructions are not under BTI control. Control flow integrity on return is based on PAC, authentication of the pointer in X30. A probable reason for this is that controlling return targets would require a BTI instruction after each call instruction (*branch with link register*). This would inflate the code and would create too many valid gadgets. Controlling RET through BTI would consequently have a negative impact on code size, performance, and security.

#### 3.1.5. Compiler support

The gcc and clang compilers support a common option named -mbranch-protection.

This option manages the various types of branch protection. To build a module with branch target identification, use -mbranch-protection=bti.

It is also possible to use -mbranch-protection=standard. This option includes all "standard" branch protection features and BTI is one of them.

#### **Function entry points**

The sample code below illustrates the prolog and epilog of a function, without and with BTI.

| Source code                               | gcc -c test.c                                                                         | gcc -c test.c -mbranch-protection=bti                               |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|

| <pre>int func1() {      return 0; }</pre> | <pre>stp x29, x30, [sp, #-16]! mov x29, sp mov w0, #0x0 ldp x29, x30, [sp], #16</pre> | <pre>bti c stp x29, x30, [sp, #-16]! mov x29, sp mov w0, #0x0</pre> |  |  |

| ŗ                                         | ret                                                                                   | ldp x29, x30, [sp], #16<br>ret                                      |  |  |

The "bti c" instruction is the only difference between the two code generations. It marks the only valid landing instruction for indirect jumps.

To make sure that the guarded page information is propagated all the way down to the linker, the compiler sets the BTI information in the special section named .note.gnu.property. This is demonstrated below, using the object file which was compiled with -mbranch-protection=bti.

\$ readelf test.o -n -x .note.gnu.property

Hex dump of section '.note.gnu.property': 0x00000000 04000000 10000000 05000000 474e5500 .....GNU. 0x00000010 000000c0 04000000 01000000 00000000 .....

| Displaying notes | found in: .note.gnu.pr | operty                 |

|------------------|------------------------|------------------------|

| Owner            | Data size              | Description            |

| GNU              | 0×00000010             | NT_GNU_PROPERTY_TYPE_0 |

| Properties       | AArch64 feature: BTI   |                        |

#### Switch / case structures

The next example illustrates the protected code for a switch / case structure.

```

int func1(int x)

{

...

switch (x) {

case 0: return 0;

case 1: return 1;

case 2: return 2;

...

case 99: return 99;

default: return -1;

}

}

```

The generated code illustrates the following differences:

- Targets of indirect calls ("bti c") vs. indirect jumps ("bti j").

- Targets of indirect branches (with a BTI instruction) vs. direct branches (without).

```

gcc -c test.c -mbranch-protection=bti

```

| target of any type of call | $\rightarrow$ | 0: bti   | С                                | ;  | function prolog            |

|----------------------------|---------------|----------|----------------------------------|----|----------------------------|

| (possibly indirect)        |               | 4: stp   | x29, x30, [sp, #-32]             | !  |                            |

|                            |               | 8: mov   | x29, sp                          |    |                            |

|                            |               |          |                                  |    |                            |

|                            |               | 18: cmp  | w0, #0x63                        | -  | test against 99            |

| direct jump                | $\rightarrow$ |          | 4e8 <func1+0x4e8></func1+0x4e8>  |    |                            |

|                            |               |          | x1, 0 <func1></func1>            | -  | •                          |

|                            |               | 24: add  |                                  | -  | (here, a computed address) |

|                            |               | 28: ldr  | w0, [x1, w0, uxtw #2             | .] |                            |

|                            |               | 2c: adr  | x1, 38 <func1+0x38></func1+0x38> |    |                            |

|                            |               |          | x0, x1, w0, sxtw #2              |    |                            |

| indirect jump @x0          | $\rightarrow$ |          | x0                               | -  | jump to computed target    |

| target of indirect jump    | $\rightarrow$ | 38: bti  | j                                | ;  | "case 0:"                  |

|                            |               | 3c: mov  | w0, #0×0                         |    |                            |

| direct jump                | $\rightarrow$ | 40: b    | 4ec <func1+0x4ec></func1+0x4ec>  | ;  | jump to epilog             |

| target of indirect jump    | $\rightarrow$ | 44: bti  | j                                | ;  | "case 1:"                  |

|                            |               | 48: mov  | w0, #0x1                         |    |                            |

| direct jump                | $\rightarrow$ | 4c: b    | 4ec <func1+0x4ec></func1+0x4ec>  | ;  | jump to epilog             |

| target of indirect jump    | $\rightarrow$ | 50: bti  | j                                | ;  | "case 2:"                  |

|                            |               | 54: mov  | w0, #0x2                         |    |                            |

| direct jump                | $\rightarrow$ | 58: b    | 4ec <func1+0x4ec></func1+0x4ec>  | ;  | jump to epilog             |

|                            |               | •••      |                                  |    |                            |

| target of indirect jump    | $\rightarrow$ | 4dc: bti | j                                | ;  | "case 99:"                 |

|                            |               | 4e0: mov | w0, #0x63                        |    |                            |

| direct jump                | $\rightarrow$ | 4e4: b   | 4ec <func1+0x4ec></func1+0x4ec>  | ;  | jump to epilog             |

| target of direct jump      | $\rightarrow$ | 4e8: mov | w0, #0xffffffff                  | ;  | "default:"                 |

| target of direct jump      | $\rightarrow$ | 4ec: ldp | x29, x30, [sp], #32              | ;  | function epilog            |

|                            |               | 4f0: ret |                                  | -  |                            |

## 3.2. Pointer Authentication Code (PAC)

## 3.2.6. PAC principles

PAC focuses on the source of illegitimate jump operations.

ROP and JOP attacks are made of jumps to unexpected locations, forming a gadget chain which usually acts as a bootstrap for some malware payload. The branch instructions are part of some valid code. However, the value of the pointers they use were somehow altered. Typically, these pointers were stored in memory (a return pointer on stack, a function address in a dispatch table) and were altered in memory after some buffer overflow attack.

The Pointer Authentication Code feature provides a way to verify that a pointer to code or data was not altered before dereferencing it.

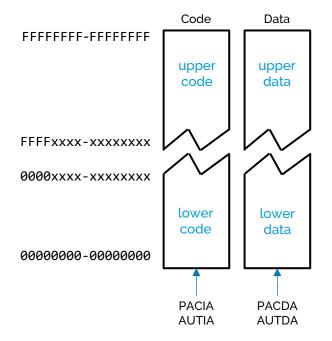

The principle is simple. On 64-bit systems, code or data pointers never use 64 bits in virtual address values. Using all bits would mean that a process addresses 16 exabytes (16 billion of billions of bytes). As of today, this is unlikely.

Consequently, PAC uses the upper bits of a virtual address to store a signature of that address.

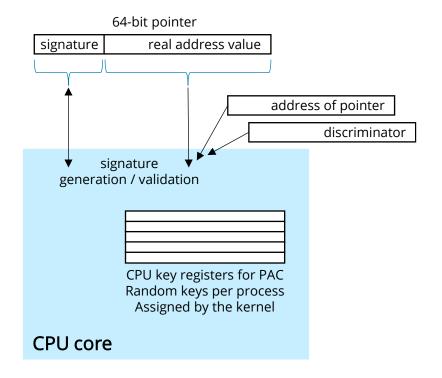

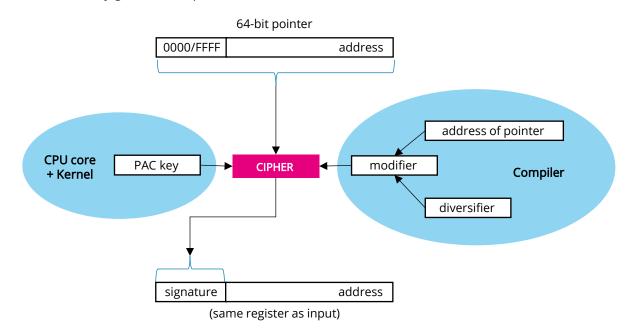

Figure 9: Pointer authentication code principles

#### Cryptographic aspects

In cryptographic terms, the PAC is a CMAC [28], a cipher-based message authentication code. It uses a symmetric cryptographic algorithm, in the CPU core hardware, to compute a CMAC-like signature.

There are five distinct special registers (2 code, 2 data, 1 generic) in the CPU which contain five possible secret keys for the PAC symmetric cipher algorithm.

These key registers are accessible at EL1 only (in kernel mode). User applications cannot read them and predict the signature of an address. This is done on purpose to prevent malicious software from forging the signature of a hacked address.

For enhanced protection, it is common to add a seed, based on the placement and semantics of the signed pointer. More on this will be found in section 3.2.13.

This is illustrated in Figure 9 above. The seed is typically a combination of the address where the pointer is stored and some semantic discriminator value.

#### Protect memory, not registers

ROP and JOP attacks overwrite data in memory. Usually, the content of registers is considered as safe. A register may load an altered value from memory but a ROP or JOP attack cannot modify the content of a register. Therefore, the signature is added to a pointer just before writing it in memory. Conversely, the signature is verified right after loading a pointer value from memory.

#### **Explicit instructions**

Adding and verifying a signature is done explicitly, using dedicated instructions which are generated by the compiler. These instructions are PACxx to add a signature and AUTxx to verify it. More complex combined instructions also exist.

The validation operation removes the signature when it is valid. Then, the register contains the plain 64-bit address. It should be noted that this is required to use the pointer. A pointer which still contains a signature is probably not a valid address and dereferencing it would generate an exception.

If the validation of the signature fails, either the pointer is left to a non-canonical address (an invalid virtual address which generates a fault) or a fault is immediately generated. The exact behavior depends on the FEAT\_FPAC feature.

## 3.2.7. Common PAC use case: function call

All PAC operations are done in the generated code of the called function. Thus, there is no interoperability issue between the caller and the callee. The caller can be compiled with or without PAC, the callee takes the responsibility of its own protection alone.

Step 1: protection.

- The function is called. The BLR instruction sets the return address in register X30, for instance:

X30 = 00000012-3456789A

- In the function prolog, a PAC instruction (e.g., PACIASP) adds an authentication code in upper bits:  $X30 = \boxed{P90E8}012 - 3456789A$

- The signed return address is pushed on stack, in the call frame.

Step 2 : authentication.

- The function epilog pops the return pointer from stack into X30. The signature is still present: X30 = D90E8012-3456789A

- X30 D30E0012-3430789A

- An AUT instruction (e.g., AUTIASP) checks the PAC and removes it if still correct:

X30 = 00000012-3456789A

- The final RET instruction returns to the caller through X30.

- Variant: if the target CPU core is Armv8.3-A or higher, one single RETAA instruction can be used instead of AUTIASP + RET.

Step 2 : in case of hack, e.g., a ROP attack exploiting a stack overflow bug.

- The altered return pointer is popped from stack into X30. If even a single bit is altered:

X30 = D90E8012-3456789B

- The AUT instruction detects the invalid PAC and leaves a non-canonical address in register X30:

X30 = 20000012-3456789B

- The final RET instruction tries to return to the caller through X30. Since the register contains a noncanonical address, an exception is generated and the hacked application crashes.

- Conclusion: the ROP attack failed.

- Variant: if the CPU core implements FEAT\_FPAC ("Fault on PAC"), the AUTIASP or RETAA instruction directly generates a fault when an incorrect PAC is detected, without waiting for the non-canonical address to be dereferenced.

#### More complex use case: tables of pointers

Consider a table of pointers which may reference data or code. It can be a switch dispatch table or a C++ vtable (the table containing the addresses of all virtual methods for a class).

- Each pointer is signed with a process-specific key. In the case of a static table, the signature is added in the initialization phase of the executable, when virtual addresses are resolved.

- In the case of C++ objects, the address of the vtable is separately signed in all object instances.

- All load, store or jump instructions using a pointer validate the signature.

- In case of JOP buffer overflow attack, the altered pointer has an invalid signature and dereferencing generates a fault.

A fully commented example of this scenario is provided in section 3.2.15.

This use case requires more care in terms of interoperability between modules which are compiled with different options. The technical tools to solve the interoperability issue are available in the Arm architecture. However, this requires the cooperation of the operating system.

Currently, this use case is implemented on macOS only. Linux leaves all tables of pointers unprotected. There is a lot of room for improvement here for the Linux kernel, gcc and clang.

## 3.2.8. PAC instructions

The three main families of PAC instructions are listed below.

- PACxx instructions compute a pointer signature and add it in the upper bits of that pointer.

- AUTxx instructions validate the signature of a pointer and remove it if it is correct.

- XPACxx instructions remove a signature without validating it. They are rarely used.

Other PAC instructions are *combined* instructions. This means that, in one instruction, they validate the signature of a pointer and, if it is correct, dereference it to branch to code (BRAx, BLRAx), return to the caller (RETAx, ERETAx) or load data (LDRAx).

The Table 6 below lists the 48 new instructions for PAC.

The 13 instructions with a blue bar on the left are in the HINT range and behave as NOP on older CPU cores which do not support PAC. Any code using only this subset of the PAC instructions is backward-compatible.

## Control Flow Integrity on Arm64 Systems

| AUTDA Xd, Xn SP | AUTIBZ          | LDRAA Xt, [Xn SP, #i]! | PACIAZ          |

|-----------------|-----------------|------------------------|-----------------|

| AUTDZA Xd       | AUTIZB Xd       | LDRAA Xt, [Xn SP, #i]  | PACIZA Xd       |

| AUTDB Xd, Xn SP | BLRAA Xn, Xm SP | LDRAB Xt, [Xn SP, #i]! | PACIB Xd, Xn SP |

| AUTDZB Xd       | BLRAAZ Xn       | LDRAB Xt, [Xn SP, #i]  | PACIB1716       |

| AUTIA Xd, Xn SP | BLRAB Xn, Xm SP | PACDA Xd, Xn SP        | PACIBSP         |

| AUTIA1716       | BLRABZ Xn       | PACDZA Xd              | PACIBZ          |

| AUTIASP         | BRAA Xn, Xm SP  | PACDB Xd, Xn SP        | PACIZB Xd       |

| AUTIAZ          | BRAAZ Xn        | PACDZB Xd              | RETAA           |

| AUTIZA Xd       | BRAB Xn, Xm SP  | PACGA Xd, Xn, Xm SP    | RETAB           |

| AUTIB Xd, Xn SP | BRABZ Xn        | PACIA Xd, Xn SP        | XPACD Xd        |

| AUTIB1716       | ERETAA          | PACIA1716              | XPACI Xd        |

| AUTIBSP         | ERETAB          | PACIASP                | XPACLRI         |

|                 |                 |                        |                 |

## Table 6: New instructions for pointer authentication code (PAC) Image: Comparison of the com

The Table 7 below details all new PAC instructions.

Some instructions are redundant for the sake of backward compatibility. When the PAC feature was specified, it was not possible to add all new instructions, with their variety of operands, in the HINT range. Instead, a few dedicated use cases were identified and the corresponding PAC instructions, with predefined operands, were reassigned in the HINT range.

#### Table 7: Detailed description of PAC instructions

| Instruction     | Description                                                                                                                                   |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| AUTDA Xd, Xn SP | Authenticate data address in Xd, using key A and modifier from Xn                                                                             |

| AUTDZA Xd       | Authenticate data address in Xd, using key A and modifier zero                                                                                |

| AUTDB Xd, Xn SP | Authenticate data address in Xd, using key B and modifier from Xn                                                                             |

| AUTDZB Xd       | Authenticate data address in Xd, using key B and modifier zero                                                                                |

| AUTIA Xd, Xn SP | Authenticate instr. address in Xd, using key A and modifier from Xn                                                                           |

| AUTIA1716       | Authenticate instr. address in X17, using key A and modifier from X16 same as AUTIA X17,X16, as a HINT instruction for "trampoline" use case  |

| AUTIASP         | Authenticate instr. address in X30, using key A and modifier from SP same as AUTIA X30,SP, as a HINT instruction for "return" use case        |

| AUTIAZ          | Authenticate instr. address in X30, using key A and modifier zero<br>same as AUTIZA X30, as a HINT instruction for (unsafe) "return" use case |

| AUTIZA Xd       | Authenticate instr. address in Xd, using key A and modifier zero                                                                              |

| AUTIB Xd, Xn SP | Authenticate instr. address in Xd, using key B and modifier from Xn                                                                           |

| AUTIB1716       | Authenticate instr. address in X17, using key B and modifier from X16 same as AUTIB X17,X16, as a HINT instruction for "trampoline" use case  |

| AUTIBSP         | Authenticate instr. address in X30, using key B and modifier from SP same as AUTIB X30,SP, as a HINT instruction for "return" use case        |

| AUTIBZ          | Authenticate instr. address in X30, using key B and modifier zero<br>same as AUTIZB X30, as a HINT instruction for (unsafe) "return" use case |

| AUTIZB Xd       | Authenticate instr. address in Xd, using key B and modifier zero                                                                              |

| BLRAA Xn, Xm SP | Branch with Link to @Xn with auth, key A, modifier Xm, ret addr => X30                                                                        |

| BLRAAZ Xn       | Branch with Link to @Xn with auth, key A, modifier zero, ret addr => X30                                                                      |

| BLRAB Xn, Xm SP | Branch with Link to @Xn with auth, key B, modifier Xm , ret addr => X30                                                                       |

| BLRABZ Xn       | Branch with Link to @Xn with auth, key B, modifier zero, ret addr => X30                                                                      |

| Instruction            | Description                                                                                                                                       |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| BRAA Xn, Xm SP         | Branch to @Xn with auth, key A, modifier Xm                                                                                                       |

| BRAAZ Xn               | Branch to @Xn with auth, key A, modifier zero                                                                                                     |

| BRAB Xn, Xm SP         | Branch to @Xn with auth, key B, modifier Xm                                                                                                       |

| BRABZ Xn               | Branch to @Xn with auth, key B, modifier zero                                                                                                     |

| ERETAA                 | Exception return, authenticate ELR, using key A and modifier from SP                                                                              |

| ERETAB                 | Exception return, authenticate ELR, using key B and modifier from SP                                                                              |

| LDRAA Xt, [Xn SP, #i]! | Load Xt with @Xn, authenticate Xn, using key A and modifier zero,                                                                                 |

|                        | pre-indexed mode => leaves Xn SP unauthenticated                                                                                                  |

| LDRAA Xt, [Xn SP, #i]  | Load Xt with @Xn, authenticate Xn, using key A and modifier zero                                                                                  |

| LDRAB Xt, [Xn SP, #i]! | Load Xt with @Xn, authenticate Xn, using key B and modifier zero,                                                                                 |

|                        | pre-indexed mode => leaves Xn   SP unauthenticated                                                                                                |

| LDRAB Xt, [Xn SP, #i]  | Load Xt with @Xn, authenticate Xn, using key N and modifier zero                                                                                  |

| PACDA Xd, Xn SP        | Compute auth. of data address in Xd, using key A and modifier Xn                                                                                  |

| PACDZA Xd              | Compute auth. of data address in Xd, using key A and modifier zero                                                                                |

| PACDB Xd, Xn SP        | Compute auth. of data address in Xd, using key B and modifier Xn                                                                                  |

| PACDZB Xd              | Compute auth. of data address in Xd, using key B and modifier zero                                                                                |

| PACGA Xd, Xn, Xm SP    | Compute in Xd the auth. of Xn using the Generic Key and modifier Xm                                                                               |

| PACIA Xd, Xn SP        | Compute auth. of instr. address in Xd, using key A and modifier Xn                                                                                |

| PACIA1716              | Compute auth. of instr. address in X17, using key A and modifier X16                                                                              |

|                        | same as PACIA X17,X16, as a HINT instruction for "trampoline" use case                                                                            |

| PACIASP                | Compute auth. of instr. address in X30, using key A and modifier SP                                                                               |

|                        | same as PACIA X30,SP, as a HINT instruction for "return" use case                                                                                 |

| PACIAZ                 | Compute auth. of instr. address in X30, using key A and modifier zero<br>same as PACIZA X30, as a HINT instruction for (unsafe) "return" use case |

| PACIZA Xd              | Compute auth. of instr. address in Xd, using key A and modifier zero                                                                              |

| PACIB Xd, Xn SP        | Compute auth. of instr. address in Xd, using key B and modifier Xn                                                                                |

| PACIB1716              | Compute auth. of instr. address in X17, using key B and modifier X16                                                                              |

| TACIDI / 10            | same as PACIB X17,X16, as a HINT instruction for "trampoline" use case                                                                            |

| PACIBSP                | Compute auth. of instr. address in X30, using key B and modifier SP                                                                               |

|                        | same as PACIB X30,SP, as a HINT instruction for "return" use case                                                                                 |

| PACIBZ                 | Compute auth. of instr. address in X30, using key B and modifier zero                                                                             |

|                        | same as PACIZB X30, as a HINT instruction for (unsafe) "return" use case                                                                          |

| PACIZB Xd              | Compute auth. of instr. address in Xd, using key B and modifier zero                                                                              |

| RETAA                  | Authenticated return, branch to @X30 with auth, key A, modifier SP                                                                                |

| RETAB                  | Authenticated return, branch to @X30 with auth, key B, modifier SP                                                                                |

| XPACD Xd               | Strip PAC from data address in Xd                                                                                                                 |

| XPACI Xd               | Strip PAC from instr. address in Xd                                                                                                               |

| XPACLRI                | Strip PAC from instr. address in X30                                                                                                              |

|                        | same as XPACI X30, as a HINT instruction for "return" use case                                                                                    |

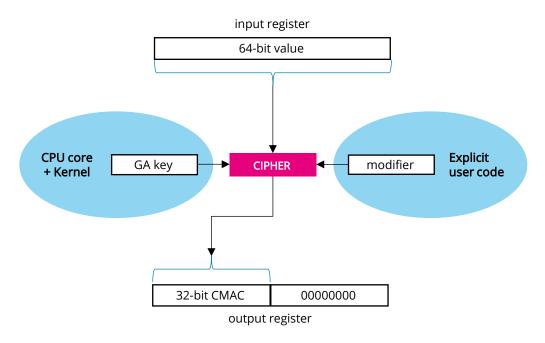

## 3.2.9. PAC cipher algorithms

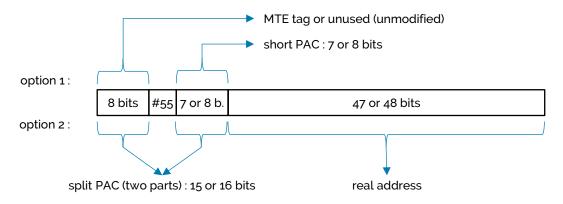

The pointer authentication code in the upper bits of a signed pointer is built using a symmetric cipher algorithm. In practice, a specific algorithm is used instead of the usual AES algorithm because the requirements for the PAC algorithm are specific:

- 64-bit input, up to 64-bit output.

- Short entropy of the input message: 47 or 48 bits.

- Short entropy of the useful part of the output: 7 to 16 bits.

- Encryption only. The decryption operation if defined is not used.

- Must be fast to compute, within the acceptable duration of an instruction.

One single cipher algorithm is hardcoded in the CPU core and is used by all PAC instructions. However, the Arm architecture specification leaves the choice of this algorithm to the implementer.

On all Arm-designed CPU cores, the algorithm is QARMA64 [12]. This is a public algorithm which was codesigned by Arm and Qualcomm.

Unlike most classical symmetric cipher algorithms, there is no mandatory number of rounds or standard substitution box ("sbox") with QARMA64.

On all initial Arm-designed CPU cores, the algorithm is QARMA5, the 5-round variant of QARMA64 (FEAT\_PACQARMA5). The Arm architecture specification also allows for QARMA3, the 3-round variant, which is faster, at the expense of security. No CPU core has been identified yet with FEAT\_PACQARMA3.

The reference implementation of QARMA64 [13] proposes three distinct substitution boxes. The Armdesigned CPU cores use the sbox number two.

Non-Arm-designed CPU cores are allowed to implement a proprietary algorithm. This is identified by FEAT\_PACIMP, as found in the so-called *Apple Silicon* chips such as Apple M1 and M2. In the case of the Apple-designed CPU cores, no public information is available on the selected algorithm.

## 3.2.10. PAC cipher keys

Just like any symmetric cipher algorithm, the PAC algorithm uses a shared secret key. The key size shall not exceed 128 bits in length. The QARMA64 algorithm uses 128-bit keys.

Because the entropy of the input (47-48 bits) and the output (7 to 16 bits) is very low, the PAC algorithm includes an additional parameter to compute the signature, called the *modifier* in the Arm architecture reference manual. In other cryptographic contexts, this kind of parameter is also named *seed*, *salt*, or *tweak*. More details on the recommended usage of the modifier are found in section 3.2.13.

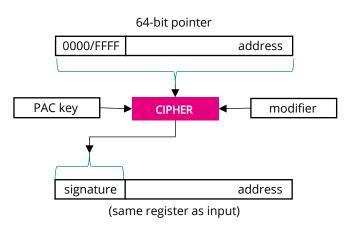

The Figure 10 below illustrates the computation process of a pointer signature.

#### Figure 10: PAC algorithm inputs and output

The key is secret. As explained in section 3.2.6, the key is stored in a special CPU register which is accessible at EL1 only (in kernel mode). The application cannot read or modify the PAC key.

#### Key life cycle